你在这里

期刊俱乐部3月15日主题:芯片封装相互作用对铜/低k互连及其他可靠性的影响

集成器件密度的指数级增长已经产生了高性能微处理器,在当前的65纳米技术中,每个芯片包含近10亿个晶体管。设备和性能的持续扩展需要在材料、工艺和设计方面进行创新,以用于后端线(BEoL)互连和封装结构。机械可靠性一直是实施新材料和新工艺的限制因素。

从1997年开始,选择铜(Cu)代替铝(Al)作为互连材料主要有两个原因:(1)铜比铝具有更低的电阻率,从而减少了RC延迟的r部分;(2) Cu的熔点比Al高,从而减少了扩散蠕变和相关的应力迁移和电迁移等可靠性问题。然而,铜互连的实现需要新的工艺,如铜电镀、damascene工艺和化学机械平面化(CMP),这导致了一系列新的可靠性问题。在90 nm技术节点(2002年左右),相对介电常数k(相对介电常数)低于二氧化硅(SiO)的介电材料2, k ~ 4),以减少RC的c部分延迟。低k介电体的实现带来了更多的挑战,至少有三个原因:(1)有许多可能的新材料,但没有明确的赢家;(2)低k材料大多力学弱(低模量、低断裂韧性);(3)低k材料的热膨胀系数失配大,粘接性差,难以与其他材料集成。随着技术的进步,互连结构不断发展,尺寸越来越小,材料和结构的复杂性越来越高。此时,微电子工业的努力重点是将超低k多孔介电材料(k < 2.5)应用到Cu互连中,以进一步降低RC延迟。与此同时,先进集成电路的封装技术也在不断发展,在倒装芯片封装中采用了塑料基板、多层高密度布线和焊球。环境安全要求从含铅焊料向无铅焊料转变,而无铅焊料更容易出现热循环疲劳和电迁移可靠性问题。

传统上,由于材料、工艺和尺寸的不同,BEoL互连和封装的可靠性问题是分开解决的。最近发现,在将硅晶片封装到塑料倒装芯片封装后,Cu/低k互连经常失效,引起了对芯片封装相互作用(CPI)的关注,这是一个关键的可靠性挑战。与独立的硅芯片不同,封装结构的热变形可以直接耦合到Cu/低k互连中,产生较大的局部应力来驱动断裂和分层(见下图)。根据焊料材料的不同,共晶Pb合金的回流温度约为160℃,锡基无铅焊料的回流温度约为250℃。在加速或循环热测试期间,温度在25°C至125°C或150°C之间变化。尽管封装的组装或测试温度大大低于芯片加工温度,但由于芯片(硅为3 ppm/°C)和封装基板(塑料基板为17 ppm/°C)之间的热膨胀系数(cte)不匹配,芯片-封装相互作用可以在互连结构中诱导非常不同的应力。焊锡球上的热诱导剪切应力在最外层焊锡排处达到最大值,并随着芯片尺寸的增大而增大。衬底填充物的使用有效地降低了剪切应力,但导致封装翘曲,导致在模具衬底填充物和模具焊点界面处产生较大的剥落应力。

解决cpi引起的可靠性问题的挑战涉及从建模、设计到制造和测试的所有领域。由于cpi引起的故障仅发生在包含Cu/低k互连的Si模具的封装组装过程之后,因此试错周期(制造和破坏)可能会很长且昂贵。基于有限元的建模以及基于断裂力学的可靠性分析已经发展起来,以了解CPI对Cu/低k互连可靠性的影响。然而,定量忠实建模作为互连和封装结构优化设计的指导,面临着巨大的挑战。这些包括:(1)从封装层(10^(-2)-10^(-3)m)到互连层(10^(-8)m)的尺寸差异很大;(2)复杂立体集成建筑;(3)材料多样,往往没有很好的表征热机械性能;(4)裂纹形核和扩展条件的不确定性。这是最近对目前的建模和实验方法以及目前对CPI效应的理解进行了回顾.下面是一份更集中的参考资料:

- G. Wang, P. S. Ho和S. Groothuis, "芯片封装相互作用:铜/低钾封装的关键问题,微电子可靠性45岁的1079 - 1093(2005)。

防止CPI诱发裂纹的一种实用方法是在芯片周围加入图案金属结构作为衬垫裂纹停止.止裂结构有效韧性的建模和实验测量对止裂结构的设计和可靠性至关重要。IBM TJ Watson研究中心的研究人员在2007年国际互连技术会议(IITC)上展示了他们的工作,总结如下:

- t.m. Shaw, E. Liniger, G. Bonilla, J. P. Doyle, B. Herbst, X. H. Liu, M. W. Lane,“裂纹止裂结构韧性的实验测定”,IEEE国际互连技术会议,第114-116页(2007)。

除了Cu/低钾技术之外,还有两项技术创新即将出现,目前正在研究中。首先,为了进一步减少RC延迟,在沟槽介电层中实施气隙已被证明是一种潜在的解决方案(例如,IBM气隙结构)。然而,如何以可接受的成本设计和制造具有令人满意的可靠性的气隙互连结构仍然是一个具有挑战性的问题。在间隙形成材料的热分解过程中,观察到在宽气隙上桥接低k帽(或硬掩膜)的坍塌。凹背和非保形填充方案的锁孔型气隙可能成为应力集中的部位,因此容易开裂。由于封装组装对脆弱的气隙结构施加额外的应力,芯片与封装的相互作用可能导致更严重的可靠性问题。下面介绍气隙互连结构的集成和可靠性问题:

- R. Hoofman, R. Daamen, J. Michelon, V. Nguyenhoang,“低k纳米多孔材料的替代方案:介电气隙集成”,固态技术49,55-58(2006年8月)。

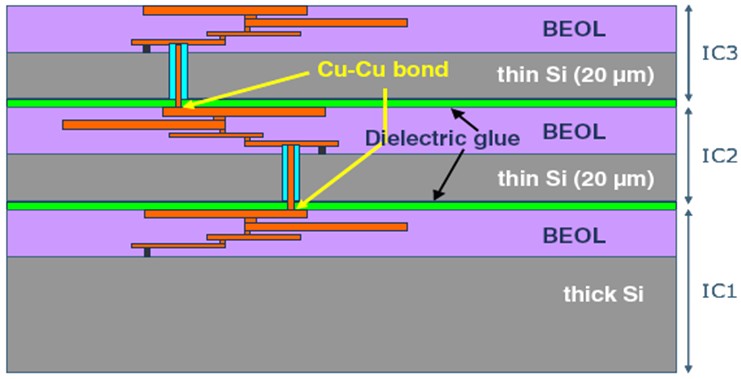

在技术路线图上,三维(3D)互连和封装的集成被认为可以显著提高芯片性能、功能和设备密度(见图)。IBM和IMEC的研究人员正在研究3D架构的关键技术挑战;下面是他们的两篇论文。机械可靠性仍然是一个关键问题,芯片封装的相互作用与3D集成具有内在的相关性。新的可靠性挑战包括:高纵横比硅通孔(tsv)的机械分支,极薄硅模的处理,堆叠晶圆之间的对齐和粘合等。力学在三维技术发展中的作用尚未确立。

在技术路线图上,三维(3D)互连和封装的集成被认为可以显著提高芯片性能、功能和设备密度(见图)。IBM和IMEC的研究人员正在研究3D架构的关键技术挑战;下面是他们的两篇论文。机械可靠性仍然是一个关键问题,芯片封装的相互作用与3D集成具有内在的相关性。新的可靠性挑战包括:高纵横比硅通孔(tsv)的机械分支,极薄硅模的处理,堆叠晶圆之间的对齐和粘合等。力学在三维技术发展中的作用尚未确立。

- W. Topol, D. C. La Tulipe, Jr. L. Shi, D. J. Frank, K. Bernstein, S. E. Steen, A. Kumar, G. U. Singco, A. M. Young, K. W. Guarini和M. Ieong,”三维集成电路, IBM Journal of Research and Development 50, 491-506(2006)。

- P. De Moor, W. Ruythooren, P. Soussan, B. Swinnen, K. Baert, C. VanHoof和E. Beyne,“IMEC 3D集成的最新进展”,Mater。Soc >,计算机协会。项目编号:0970-Y01-02(2006)。

| 附件 | 大小 |

|---|---|

| 616.21 KB | |

| 331.26 KB | |

| 1.74 MB | |

| 1.41 MB |

工业问题对学术界的重要性

亲爱的芮:非常感谢你对这个问题的精彩介绍。读了你的帖子让我想起了学者走出论文和书籍,去拜访公司,和工程师讨论他们的问题是多么重要。在相互联系的机制方面,有两件特别的作品给了我很大的启发。当其他人遇到具有工业意义的新问题时,研究它们可能会提供一个视角。

R.H.道斯卡德,M.莱恩,Q.马和N.克里希纳,多层薄膜结构的粘接与脱粘.工程断裂力学,61 - 62(1998)。本文发展了四点弯曲法。虽然力学和技术本身在当时已经为人所知,但斯坦福大学的Reiner Dauskardt和英特尔的Qing Ma之间的合作,确实将界面断裂力学降到了工业实践中。他们的方法现在被业界广泛采用。这项工作大大提高了微电子工业对断裂力学的认识。

M.A. Korhonen, P. Borgesen, Tu . K.N., Li . yy,受限金属线中电迁移引起的应力演化.j:。物理学报,73,3790(1993)。这是康奈尔大学和IBM合作的成果。同样,当这篇论文发表时,大部分的基本成分都是已知的。但作者把这些成分放在一起,并清楚地将电迁移与互连结构的机械行为联系起来。本文为后续的电迁移分析奠定了基础。

这两项工作在我们研究低k互连结构时仍然很重要。

资源,了解半导体行业的挑战

这里有两个资源:

粘附和电迁移

志刚是绝对正确的。我在普林斯顿开始和他一起研究这个领域。在奥斯汀大学,通过我的同事,何志强在美国,我经常受到来自工业领域的机械问题的挑战。我们现在正在与几家公司合作解决各种问题,包括CPI、气隙、3D等。

志刚提出的两篇论文确实是重要的作品,是技术开发中学术与产业合作的典范。4点弯曲法现在是附着力测量的行业标准。该方法被IBM小组(Shaw等人,IITC 2007)用于表征裂纹止裂结构的韧性。Wang等人(2005)采用了类似的方法,混合模双悬臂梁,来表征低k与其他材料之间的界面粘附性。同样,这种方法已经为学术界所熟知10多年了。与4-pt弯曲不同,混合模态DCB试验可以测量全范围的模态混合(从I模态到II模态)的界面韧性。

Korhonen等人在电迁移方面的工作通过一个简单的一维模型提供了对该问题的基本理解。许多更复杂的模型已经被开发出来。同样重要的是电迁移测试,比如德克萨斯大学奥斯汀分校Paul Ho的团队开发的测试。电迁移对于使用硅通孔(tsv)和金属焊盘键合的3D电路非常重要,尽管其几何形状与金属线不同。

RH

孔隙度对低钾多孔性黏结断裂能的影响

感谢Rui提出多孔超低k材料的脆弱性问题。在过去一年左右的时间里,我们小组一直在研究孔隙度对多孔低钾薄膜力学性能的影响,主要是对粘性断裂能和刚度的影响。采用双悬臂梁法测量断裂能,采用椭偏法测量孔隙率。我们注意到不同孔隙度的薄膜也会有不同的基质性质。在分离出基体差异造成的影响后,发现整体黏结断裂能降低线性随着孔隙率的增加,人们可以从混合规律和透孔平面开裂机制中得到期望,这与以前的一些报道有所不同。例如,Guyer等人(JMR 2006)。(21(4): p. 882-894.)报道了一些自旋MSQ尺度的内聚断裂性能与平均膜密度(孔隙率)的经验幂律关系幂指数等于2.

我们将在即将到来的MRS春季会议上报告我们的结果。欢迎评论和讨论。

李韩

RE:孔隙度对黏结断裂能的影响

李涵,你有没有研究过破坏强度与孔隙率的关系?

哦,我想你是说

哦,我想你是说屈服强度吧?不,我们没有特别研究过,部分原因是薄膜非常脆。

李韩

全球和本地的驱动力

亲爱的黄教授,这是一个非常有启发性的关于CPI带来的机械挑战的总结,因为你以一种紧凑而清晰的方式描述了这个领域。非常感谢。

和我的小组成员一起张甄和Juil Yoon由于CPI,我对半导体行业的可靠性问题很感兴趣。从你的描述和我的理解来看,有两种驱动力共同导致Cu/低k互连的失败:由于局部材料和几何形状的不连续而导致的局部驱动力,即已经存在于独立硅模中的驱动力,例如Cu和低k材料之间的不匹配;另一方面,芯片安装到封装基板后,由于硅晶片与塑料封装之间的不匹配而产生的全球驱动力。我用“局部”和“全局”来区分这两种驱动力,因为倒装芯片封装的层次结构有很大的维度变化。那么问题来了:

1.这两种驱动力应该以何种方式叠加?线性的还是更复杂的?

2.其中一个是否会凌驾于另一个之上,以至于在某些情况下,它会足够准确地放弃不重要的那个?

的确,有限元计算还有k场分析通过张甄等人发现微小的水平界面裂纹的能量释放率主要来自全局驱动力的贡献,这就解释了为什么芯片封装后会发现更多的故障。我发现这是值得注意的,因为如果全局驱动力总体上压倒了局部驱动力,可以避免全局-局部子层次建模,结果仍然令人满意。

回复:全球和本地驱动力

>

谢谢你的评论。本地和全球驱动力的分离是有益的。与传统处理一样,互连结构必须首先通过芯片级测试才能在本地驱动力中生存下来。在封装过程之后,组装必须在封装级测试的全球驱动力中存活下来。这种做法被发现对于使用二氧化硅(SiO2)作为后端电介质的芯片是足够的,但对于低k和超低k电介质则不是这样。原因可能有两方面:(1)低k介电体力学性能较弱,更容易断裂;(2)由包装工艺和结构引起的全球驱动力可能不同。由于Cu/低k互连可能已经通过了芯片级测试,CPI研究通常忽略了局部驱动力。然而,为了确定互连层的全局驱动力,多级子建模仍然是必要的。通过比较裂纹尺寸和互连的特征尺寸,可以了解封装级别k场分析的局限性。 As we all know, the K-field in the linear elastic fracture mechanics is only valid within an annular region, far from any material or geometrical boundaries. Such boundaries are all over the interconnect structure, such as Cu/low k interfaces. In essense, the global k-field may be considered as the loading parameter imposing onto the local interconnect structure, whereas the detailed stresses and fracture driving forces at various interfaces must be determined. This is in the same spirit as submodeling, although more than two levels (with 2-3 intermediate submodels between global and local) are often needed from numerical perspectives.

RH

回复:全球vs本地

嗨,瑞,

很高兴你这个月提出了这么好的话题。许多好的论文和要点需要消化。非常感谢。

根据你的评论,我不明白为什么包装过程引起的全球驱动力是不同的,如果只是互连堆栈的变化。互连内部的局部不匹配或微观结构是否会影响由模具、封装、盖等引起的整体应力场?这里有一个类比:我们知道重力影响地球上的一切,而且这种影响是巨大而明显的。但是,如果我们建一个家或实验室或任何地方结构呢?这些局部结构会反过来影响重力吗?我怀疑。因为长度尺度和质量尺度。同样的道理也适用于这里。

其次,由全局失配引起的k场主导整个互联区域。k-环空的大小与模具厚度或包笼厚度或下填料厚度的大小有关,即全局参数。正如我们研究多晶材料一样,当我们考虑整体应力场时,通常不考虑各向异性效应的影响,除非我们考虑晶粒周围或晶界等的局部应力。同样,正如我们将断裂力学应用于多晶材料一样,如果将其作为均质各向同性材料,当裂纹远大于晶粒尺寸时,裂纹驱动力不是晶粒尺寸的函数。微观组织的变化,如晶粒尺寸的变化,影响材料的强度、韧性等性能,但不影响裂纹驱动力。

因此,如果我们回到倒装芯片封装,我认为同样的推理仍然适用。只要采用介电常数更低的ILD, Cu/低k互连就会越来越弱,即断裂韧性变弱。但在全局参数不变的情况下,由于切割引起的裂纹尺寸(可达~10um)远大于互连中的特征尺寸,则裂纹驱动力变化不大。这让我想起了Michael Lane在粘附学会2008年会议上的演讲。在他们的计算中,无论裂纹位于哪个界面,无论使用哪种低k材料(low-k 3.0, ULK2.4, ULk2.2等),能量释放率几乎在同一曲线上。

正如Rui所说,如果裂缝尺寸与互连中的特征尺寸在同一数量级上,则需要多尺度或多层子模型。例如,互连线在焊点附近的裂纹,互连线内部的缺陷通常较小,尺寸与局部特征相似。在这种情况下,需要进行多尺度子建模。

如果我说错了请指正。

真诚地,

甄

互连层封装驱动力(本地)

你好,

你把重力类比得有点离谱。我绝不是在暗示本地互连结构会显著影响封装层面的全球驱动力。然而,当我们讨论互连层的断裂时,局部材料结构很重要。k-环空足够大,可以包围整个互连区域,但由于分析是基于均匀化模型,因此它不能给出特定界面破裂的详细信息(例如M1 vs M5)。研究发现,上层互连层的界面更容易断裂,特别是当上层有选择地使用低k材料时。然而,观察似乎表明,在上层成核的裂纹可能会扩展到较低的水平,这可能会对前端器件造成进一步的破坏。为了模拟互连结构中的裂纹扩展,需要同时考虑断裂驱动力和模态组合。至少对我来说这是一个很大的挑战。

RH

切丁时塞子破裂

嗨,瑞,

这是一个很好的话题,文献很好地代表了这个领域。模具边缘的裂纹塞不仅可以偏转或阻止裂纹的扩展,而且可以防止水分扩散到模具的中心。由于ULK多孔材料的高水扩散率,这一点尤为重要。

近十年来,集成电路力学研究大多集中在亚临界或“慢”速度裂纹扩展行为上。我想知道这些实验的断裂结果是否适用于芯片的高速切割过程中观察到的失效-这是封装的第一步。如果我们可以通过高速锯最小化损坏区域,我们可以减少划线线宽度(即每个晶圆更多的芯片)和缺陷的产生。我知道参数,如锯片速度和锯片几何形状,是非常重要的,但似乎很少有坚实的力学理论在这个领域的发展-高速冲击断裂在纳米尺度。也许你对慢速骨折和高速小型骨折的区别有更多的经验。

停

有更详细的切片描述吗?

亲爱的Ting:我对你对切片的描述很感兴趣。你能更详细地描述一下这个问题吗?就晶圆浪费和可靠性而言,问题有多严重?你有推荐信吗?这个问题听起来很适合进行理论和实验的联合研究。

一些论文

你好中国,

这里有两篇关于CPI的论文和一些实验图片。切丁引起的分层是巨大的。

刘晓华等,[IITC 2007]

Lane M等人@ 2008年粘连年会。

切丁

你好中国,

这对于行业来说是非常重要的,因为在模具边缘有相当多的努力和“房地产”被分配给骰子。如果能在这方面有一个很好的理解,公司可以在彼此更近的地方打印芯片,并在每个晶圆上生产更多的产品。高速断裂似乎是一个很难理解的问题,因为很难“视觉化”实际的断裂。分层是最常见的失效模式,但硅裂纹也经常被报道。IBM论文列表张甄都是很好的例子。

问候

停

微/纳米机械和热疲劳

谢谢你,芮。这是一个很好的话题。我从这里的讨论中学到了很多。随着互联的不断缩小,纳米力学的作用越来越重要。我可以看到互连的机械和热疲劳等问题。我做了一些MEMS/NEMS中硅纳米结构的纳米疲劳实验(见下文)。

李晓东和Bharat Bhushan,“基于纳米压痕技术的MEMS/NEMS纳米结构疲劳研究”,中国机械工程,(2003):503-508。

我想看看有没有关于连接点疲劳的论文。我想多了解一下这个话题。谢谢你的帮助。

互连和封装的疲劳

小东,

谢谢你的论文。我不熟悉任何关于互连体疲劳的研究。热循环是互连和封装结构的标准测试,热循环下的一些失效机制已经得到了研究,其中可能包括疲劳以及其他机制。例如,Zhigang和他的同事们发现了一种棘轮机制,这种机制会导致金属互连上的脆性钝化膜在热循环后断裂。下文中还提到了其他几种失效模式:

黄明,索之,马麒,"薄膜结构中塑性棘轮引起的裂纹".固体力学与物理学报,50; 1079-1098(2002)。

RH

Re:互连和封装疲劳

谢谢你瑞。我刚看了报纸

黄明,索之,马麒,"薄膜结构中塑性棘轮引起的裂纹".固体力学与物理学报,50; 1079-1098(2002)。

这篇论文对我理解塑性变形和裂纹萌生有很大帮助。我会跟进做更多的实验,希望以后能在这里报告一些结果。

薄膜的热疲劳

鲍勃·凯勒的评论让我想起了他们关于金属薄膜和互连的热疲劳的作品。

RH

CPI损害补救

所谓的芯片封装相互作用(CPI)效应是我在摩托罗拉的同事雷·梅尔卡多博士在1999年底和2000年初首次发现的。当时,Cu-oxide back - end -of- line (BEOL)是合格的。摩托罗拉半导体产品部门(现在的飞思卡尔半导体)正在研究低铜k BEOL。我们发现,即使经过长时间的努力优化低k集成工艺,当封装好的模具(通过探针测试)时,封装成品率非常低。晶圆厂的人责怪包装人,包装人说没有改变包装工艺流程。Lei的有限元模型显示,在热载荷作用下,封装产生的裂纹驱动力(能量释放率)可以高达独立晶圆的一到两个数量级。此后,行业开始认识到CPI效应。这是一个古老的故事。教授们的评论很好地总结了最近的发展。何和黄。

今天,我认为大多数致力于低k BEOL的公司都知道如何减轻CPI带来的损害。围绕减排方案有很多专利申请。补救措施主要分为两大类。一是芯片的优化。另一个是包装的优化。在芯片方面,我们可以在工艺优化方面做很多事情,以构建更坚固的界面,生产更强的低k材料。另一个技巧是在BEOL中放置假结构以阻止IC设计布局中的裂缝,这当然是一个很好的专利主题。从封装方面,可以为倒装芯片凸起选择合适的焊料合金(较软)和合适的下填充材料(CTE匹配焊料)。讨论包装优化的一些很好的论坛是ECTC (www.ectc.net)及ITherm (www.itherm.org)。

我最近意识到一些芯片设计软件开发人员正试图将IC布局优化构建到他们的软件工具中。然而,原始版本倾向于优化布局,以尽量减少对独立晶圆的压力。CPI的影响完全被忽略了。这可能会导致糟糕的布局设计,这是很危险的。

我很高兴iMecha万博manbetx平台nica选择这个话题作为这个月杂志俱乐部的主题。我希望越来越多的机械师关注真实的行业问题,万博体育平台比如CPI问题。

超过Cu/低k

亲爱的杰夫,

非常感谢您的评论。我同意你的观点,学术界和工业界在技术发展的实际问题上合作是很重要的,这与志刚之前的评论相呼应。特别是,由于CPI对Cu/低k互连的影响现在已经被业界很好地理解,那么Cu/低k技术之外的实际问题是什么?像你这样的工业研究人员的评论将对发展学术界和工业界之间的合作非常有帮助。

RH

CPI对金融的影响

瑞,

CPI的另一个重要之处在于它的金融影响。全球半导体行业每年的总收入为2700 - 3000亿美元。Cu-low-k BEOL主要应用于cpu、gpu、dsp、无线应用芯片、电信基站芯片等高性能器件中。如果我们计算一下英特尔、AMD、IBM、英伟达和TI的收入,我们就会知道,每年有超过500亿美元的产品涉及到CPI效应。这是一个很好的例子,说明像雷·梅尔卡多博士这样的机械师如何对经济万博体育平台产生影响。

杰夫

消费者价格指数

我想插句话来附和杰夫的观点。

CPI对半导体行业有许多财务影响。当它首次成为90nm节点的主要良率和可靠性问题时,它迫使业界争相采用低tg下填充,这将使焊料凸起面临更大的危险,或者采用芯片级工艺变化来降低风险,例如在氮化钝化或裂纹停止中添加聚酰亚胺应力缓冲。所有这些努力都将影响产量或将可靠性问题转移到其他地方。

我个人仍然认为,一旦我们迁移到ULK和无铅游戏,CPI问题就不会完全消失。然而,我们确实有了更高的信心,因为我们现在有了很好的理解。

Philip Garrou博士关于3D集成的博客

点击http://www.semiconductor.net/blogger/3068.html以了解3D技术的最新发展。

RH